Engenheiros da Universidade de Stanford, da Universidade Carnegie Mellon, da Universidade da Pensilvânia e do Instituto de Tecnologia de Massachusetts trabalharam com a SkyWater Technology, a maior fundição de semicondutores exclusivamente americana, para criar um novo chip de computador multicamadas. A equipe diz que sua arquitetura pode marcar uma grande mudança no hardware de inteligência artificial e impulsionar a inovação doméstica em semicondutores.

Ao contrário da maioria dos chips atuais, que são em sua maioria planos e bidimensionais, este protótipo foi construído para crescer. As peças ultrafinas são colocadas como os pisos de um edifício alto, e a fiação vertical funciona como muitos elevadores de alta velocidade que movem grandes quantidades de dados rapidamente. Com um número recorde de interconexões verticais e um layout bem integrado que coloca a memória e as unidades de computação próximas umas das outras, o design evita as lentidão que limitaram o progresso em chips planares. Em testes e simulações de hardware, o chip 3D supera os chips 2D em cerca de uma ordem de grandeza.

Os pesquisadores já fizeram chips 3D experimentais em laboratórios acadêmicos antes, mas a equipe diz que esta é a primeira vez que os chips apresentam melhorias claras de desempenho e são produzidos em uma fundição comercial. “Isso abre a porta para uma nova era de fabricação e inovação de chips”, disse Subhashish Mitra, William E. Iyer Professor de Engenharia Elétrica e Professor de Ciência da Computação na Universidade de Stanford e investigador principal de um novo artigo que descreve o chip apresentado no 71º Encontro Anual Internacional de Dispositivos Eletrônicos do IEEE (IEDM). “Essas inovações permitem um aumento de 1.000 vezes no desempenho do hardware que os futuros sistemas de inteligência artificial necessitarão”.

Por que os microcircuitos planos lutam com a inteligência artificial moderna

Grandes modelos de IA, como ChatGPT e Claude, movem constantemente grandes quantidades de dados entre a memória que armazena as informações e as unidades de computação que as processam.

Nos chips 2D convencionais, tudo está em uma superfície e a memória é limitada e dispersa, de modo que os dados são transferidos por um pequeno número de caminhos longos e lotados. As peças de computação podem funcionar muito mais rápido do que os dados podem ser entregues, e o chip não consegue manter memória suficiente por perto. O resultado é uma espera frequente. Os engenheiros chamam esse problema de “parede de memória”, onde a velocidade de processamento excede a capacidade do chip de transferir dados.

Durante anos, os fabricantes de chips resistiram à parede da memória, encolhendo os transistores, os minúsculos interruptores que realizam cálculos e armazenando dados, e colocando mais deles em cada chip. Mas os pesquisadores dizem que esta abordagem se aproxima dos limites físicos conhecidos como “muro da miniaturização”.

O novo design visa superar ambos os limites através da construção ascendente. “Ao integrar verticalmente a memória e a computação, podemos mover muito mais informações com muito mais rapidez, assim como os elevadores em prédios altos permitem que muitos residentes se movam entre os andares ao mesmo tempo”, disse Tathagata Srimani, professor assistente de engenharia elétrica e de computação na Carnegie Mellon University, autor sênior do artigo, que começou como pós-doutorado com Mitra.

“A parede da memória e a parede da miniaturização formam uma combinação mortal”, disse Robert M. Radway, professor associado de engenharia elétrica e de sistemas na Universidade da Pensilvânia e coautor do estudo. “Nós atacamos isso de frente, integrando firmemente memória e lógica e, em seguida, construindo em cima com densidade extremamente alta. É como a Manhattan da computação: podemos acomodar mais pessoas em um espaço menor.”

Como é feito um chip 3D monolítico

Muitos esforços anteriores para criar chips 3D seguiram o caminho mais simples de montagem de chips individuais. Isso pode ajudar, mas as conexões entre as camadas costumam ser relativamente grosseiras, em número limitado e podem se tornar gargalos.

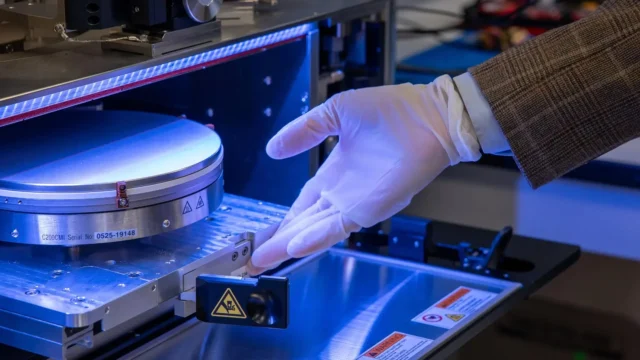

Esta equipe adotou uma abordagem diferente. Em vez de fabricar chips individuais e juntá-los, eles constroem cada nova camada diretamente sobre a anterior em um fluxo contínuo. Este método, conhecido como integração 3D “monolítica”, utiliza temperaturas suficientemente baixas para evitar danos aos circuitos já construídos abaixo. Isso permite que as camadas sejam embaladas com mais firmeza e criem ligações muito mais estreitas entre elas.

O ponto chave, dizem os pesquisadores, é que todo o processo foi realizado em uma fundição comercial nacional de silício. “Transformar um conceito acadêmico avançado em algo que uma fábrica comercial possa construir é um enorme desafio”, disse o coautor Mark Nelson, vice-presidente de desenvolvimento de tecnologia da SkyWater Technology. “Isso mostra que essas arquiteturas avançadas não são possíveis apenas no laboratório – elas podem ser produzidas internamente, em escala, que é o que a América precisa para permanecer na vanguarda da inovação em semicondutores.”

Ganhos de desempenho e o que vem por aí para hardware de IA

Nos primeiros testes de hardware, o protótipo superou chips 2D comparáveis por um fator de cerca de quatro. Simulações da equipe sugerem ganhos ainda maiores à medida que o design cresce com mais memória e camadas de computação. Com camadas adicionais, os modelos apresentam uma melhoria de até doze vezes nas cargas de trabalho de IA do mundo real, incluindo cargas de trabalho derivadas do modelo Meta LLaMA de código aberto.

Os pesquisadores também enfatizam a recompensa de um intervalo maior. Eles dizem que a arquitetura oferece um caminho prático para uma melhoria de 100 a 1.000 vezes no produto de atraso de energia (EDP), uma medida que combina velocidade e eficiência energética. Ao encurtar a distância de transferência de dados e adicionar muito mais caminhos verticais para percorrer, o chip pode aumentar a largura de banda e, ao mesmo tempo, reduzir a energia por operação, o que tem sido difícil de conseguir com projetos planares convencionais.

A equipe diz que o trabalho não envolve apenas velocidade. Ao demonstrar que chips 3D monolíticos podem ser fabricados nos Estados Unidos, eles dizem que isso fornece um modelo para um novo período de inovação de hardware nacional, onde chips de última geração podem ser projetados e fabricados em solo americano.

Eles também dizem que a mudança para a integração 3D vertical e monolítica exigirá uma nova geração de engenheiros treinados na técnica, assim como o boom dos circuitos integrados da década de 1980 foi alimentado por estudantes que estudavam design e fabricação de chips em laboratórios dos EUA. Por meio de colaborações e esforços de financiamento, incluindo o Microelectronics Commons California-Pacific-Northwest AI Hardware Hub (Northwest-AI-Hub), estudantes e pesquisadores já estão se preparando para promover a inovação em semicondutores americanos.

“Tais avanços estão, obviamente, relacionados com a produtividade”, disse H.-S. Philip Wong, professor Willard R. e Inez Kerr Bell da Stanford School of Engineering e investigador principal do Northwest AI-Hub. “Mas também tratam de oportunidades. Se pudermos criar chips 3D avançados, poderemos inovar mais rapidamente, responder mais rapidamente e moldar o futuro do hardware de IA.”

Esta pesquisa foi conduzida na Escola de Engenharia da Universidade de Stanford, na Faculdade de Engenharia da Universidade Carnegie Mellon, na Escola de Engenharia e Ciências Aplicadas da Universidade da Pensilvânia e no MIT, e todos os produtos foram concluídos na fundição da SkyWater Technology em Bloomington, Minnesota. O apoio foi fornecido pela Defense Advanced Research Projects Agency, pelo US National Science Foundation Graduate Fellowship Program, pela Samsung, pelo Stanford Precourt Institute of Energy, pela Stanford SystemX Alliance, pelo Departamento de Defesa Microelectronics Commons AI Hardware Center, pelo Departamento de Energia dos EUA e pelo programa Future of Semiconductors da National Science Foundation (2425218).

Coautores adicionais de Stanford incluem Soohyun Choi, Samuel Dayo, Andrew Bechdolt, Shengman Li, Dennis T. Rich e RH Yang. Autores adicionais da CMU e MIT.